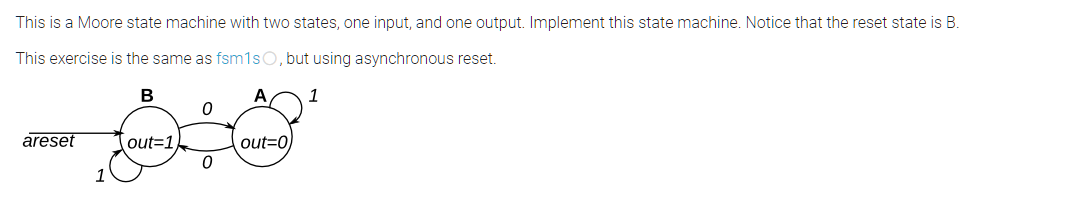

module ab(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case(state)

B:begin

if(in == 0)begin

next_state =A;

end

else begin next_state = B;end

end

A:begin

if(in == 0)begin

next_state = B;

end

else begin

next_state =A;

end

end

default:begin

next_state = B;

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset)begin

state <=B;

end

else begin

state <= next_state;

end

end

// Output logic

// assign out = (state == ...);

assign out = (state == B)?1‘b1:1‘b0;

endmodule

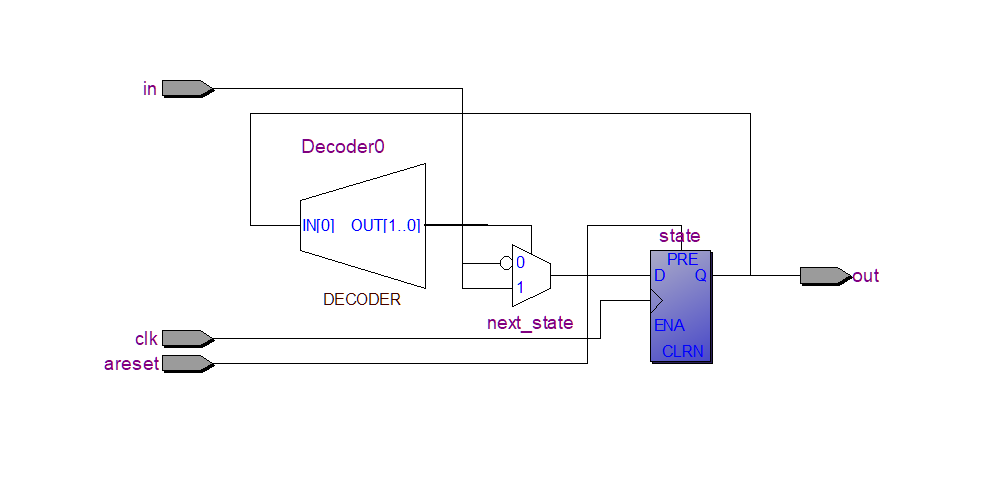

3 原理图

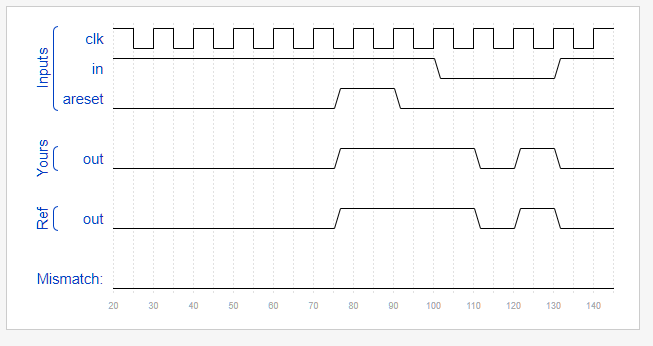

4 仿真

题源:题源:FSM1

原文:https://www.cnblogs.com/waqdgstd/p/15166301.html