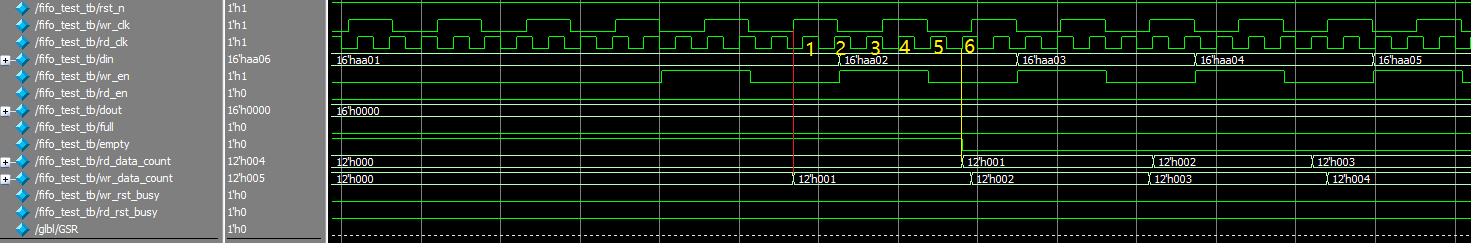

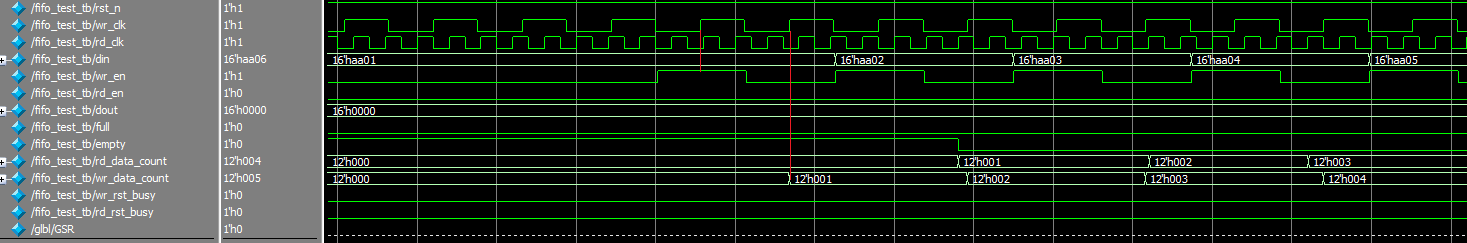

异步时钟FIFO独有的值

表示FIFO 读时钟域的 empty拉低的时间

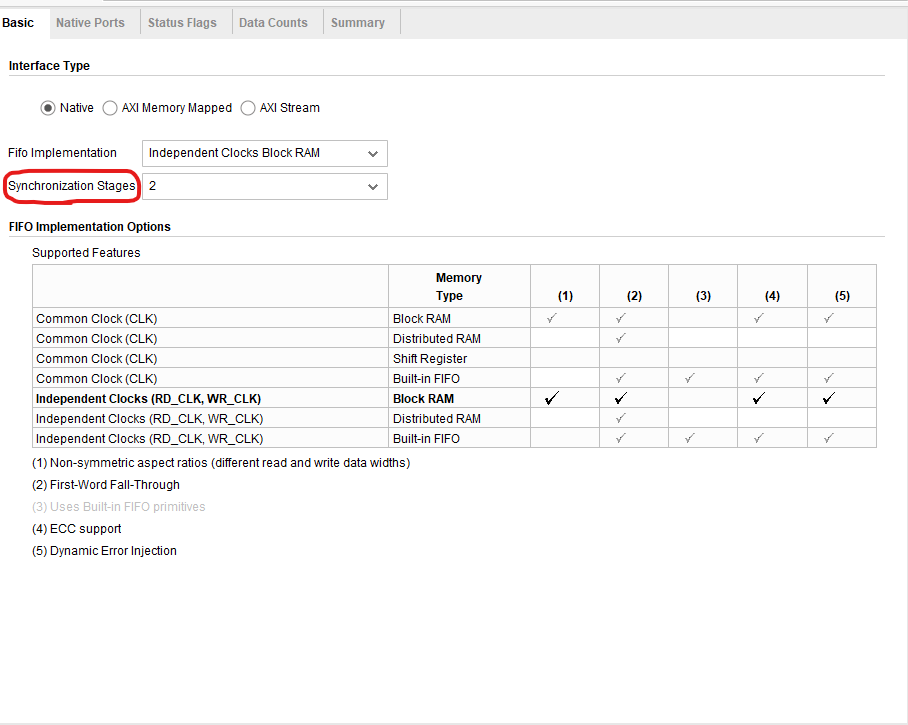

当 synchronization stages = 4时

在write_data_count被写入值后,经过(synchronization stages + 2) = 4个读时钟上升沿,拉低empty且read_data_count+1,表示可以开始读了

写时钟第一个上升沿检测到读使能,写入一个数据

写时钟第二个上升 write_data_out + 1

原文:https://www.cnblogs.com/cnlntr/p/14437878.html