|

特性 |

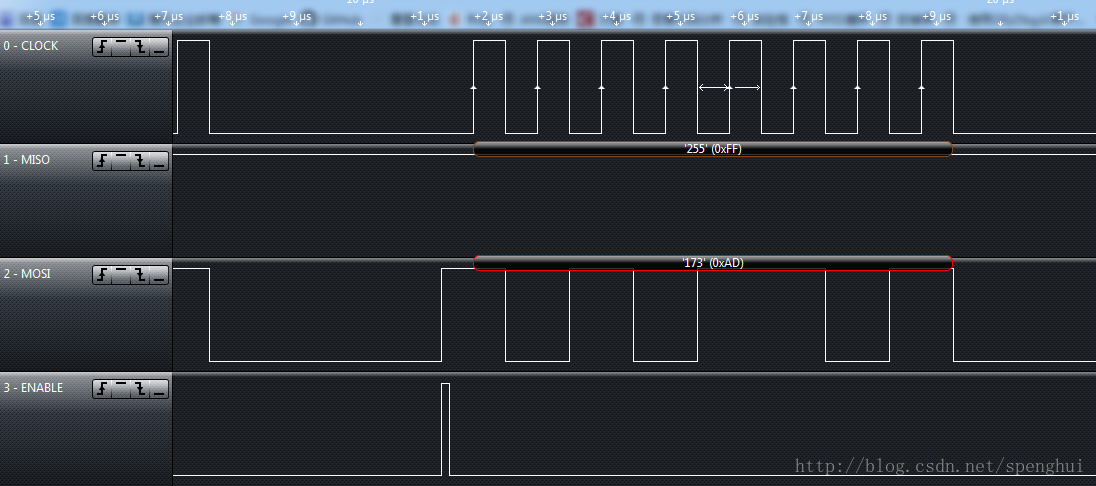

SPI |

IIC |

UART |

|

同步/异步 |

同步(采用时钟沿,进行数据采样) |

异步 |

异步 |

|

传输速率(bps) |

10M(一般是MHZ,主要看实际配置的CLK) |

<=400K |

20k |

|

硬件连线 |

CS,CLK,MISO,MOSI |

SCL,SDA |

RX,TX,GND |

|

拓扑结构 |

星形,拓扑形 |

星形 |

NA |

|

硬件原理 |

|

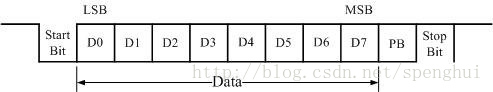

START(SCL高电平,SDA下降)/器件地址/写or读/ACK/数据地址/ACK/数据/ACK/STOPT(SCL高电平,SDA上升)

|

|

|

上下拉 |

MOSI需要加匹配电阻 |

SCL.SDA上拉(4.7k-10k) |

NA |

|

|

|

|

|

原文:https://www.cnblogs.com/hao-li/p/14298953.html