低功耗简单知识

1、低功耗分类?

分为静态功耗和动态功耗;

2、低功耗技术

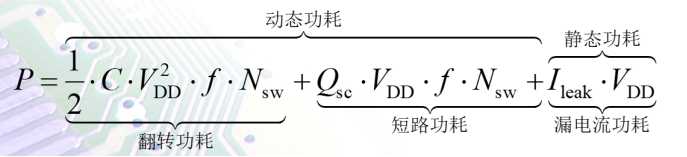

公式:Power = K*F*C*V^2,功率=系数*频率*负载电容值*电压平方

(1)控制工作频率

(2)减少电容负载

(3)降低工作电压

3、下列属于常用的低功耗设计方法是(ABCD)

A、时钟门控

B、多电压设计

C、降低电源电压

D、动态电压和频率调节

4、下面降低功耗的方法中,属于降低静态功耗的有(ADE)(不一定对)

A:门级电路的功耗优化

B:多阈值电压

C:门控时钟电路

D:操作数分离

E:多个供电电压

5、ASIC中低功耗的设计方法和思路(不适用于FPGA)

合理规划芯片的工作模式,通过功耗管理模块控制芯片各模块的Clock,Reset起到控制功耗的目的。

6、CMOS的功耗组成是什么样的?

功耗组成:动态功耗和静态功耗组成;

(1)动态功耗:开关功耗和短路功耗;

(2)静态功耗:主要是漏电流引起的功耗

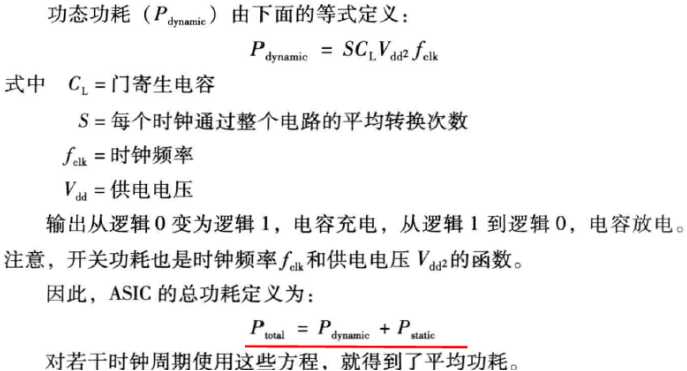

低功耗设计

浪涌、静态功耗和动态功耗是主要的三个功耗源。

浪涌电流指的是器件上电时产生的最大瞬时输入电流,在应用中也称为启动电流,其与设备相关。例如基于SRAM的FPGA就有很突出的浪涌电流,因为上电时需要这些器件的配置过程,从外部存储器下载数据配置编译资源等。

静态功耗又称为待机电流产生的功耗。待机电流指的是关断主电源或者系统进入待机模式下产生的电流。与浪涌电流类似,其与电子元件的电气特性密切相关。静态功耗也包括电路中由晶体管的漏电流所导致的功耗。

动态功耗或者开关功耗是门电路输出切换时,由逻辑转换所引起的功耗。

动态功耗在大规模IC设计中占主要地位,典型的应用中动态功耗占用了总功耗的80%。

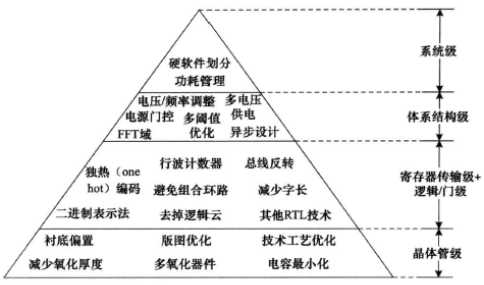

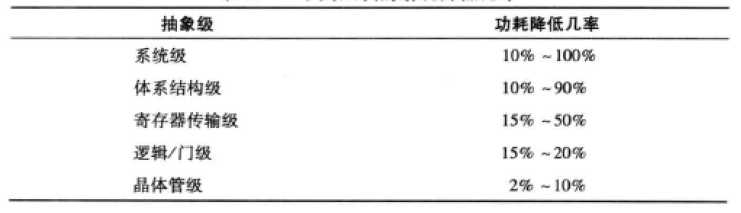

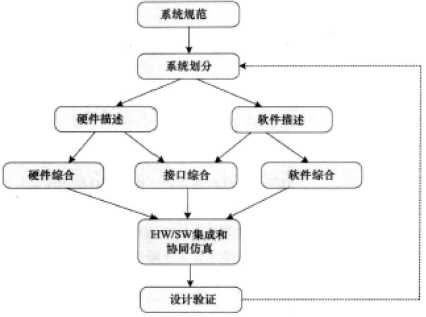

降低功耗应当在所有的设计层次上进行,即在系统级、逻辑级和物理级。层次越高对功耗降低就可能越有效。如图所示2.1为在不同设计层次上降低功耗的各种设计技术。

图2.1 层次级低功耗设计

图2.2 功耗降低概率对比

在设计系统前,必须对系统及其性能以及功耗的目标作以考虑。

图2.3 软硬件划分流程

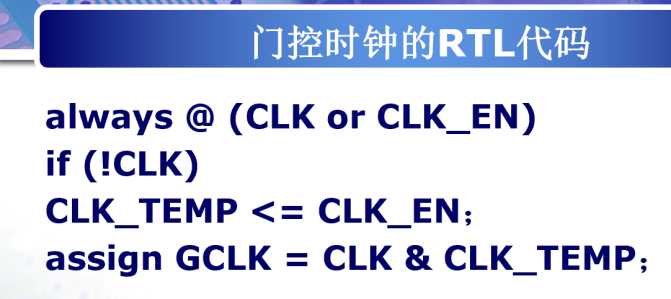

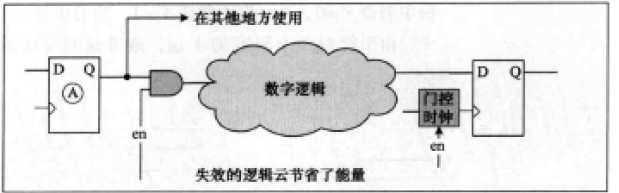

高级门控时钟:在同步数字系统中,时钟分布贡献了整个数字开关功率的绝大部分。在许多情况下可以通过门控时钟将绝大部分不使用的电路关闭掉。

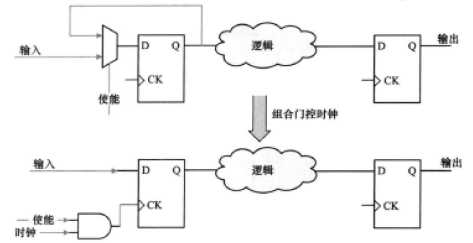

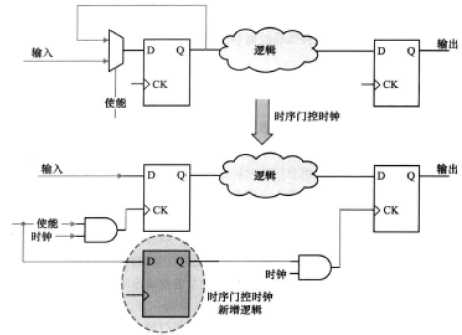

门控时钟,以前讲过组合门控时钟,即图2.4所示,由于其是在输出不变时使触发器的时钟失效,因此他可以降低5%-10%的动态功效,而时序门控时钟在不影响设计功能的情况下改变设计结构,其能够减少连接到带有门控时钟的寄存器块的设计部分的冗余切换。如图2.5所示为时序门控时钟。

图2.4 组合门控时钟

图2.5 时序门控时钟

不过时序门控时钟电路最大的挑战在于识别出流水线上“多余的”或者“不关心”的状态,一旦这一工作完成,将会大大将降低功耗,约15%-25%,不过在多于16触发器情况下使用更好。

在进行系统设计时,RTL完成时80%的功耗已经确定。后端流程不能解决所有功耗问题,因此需要系统性地直接从RTL中或从映射结果中寻找降低功耗的机会,微架构和RTL代码风格对于动态与静态功耗有极大的影响。

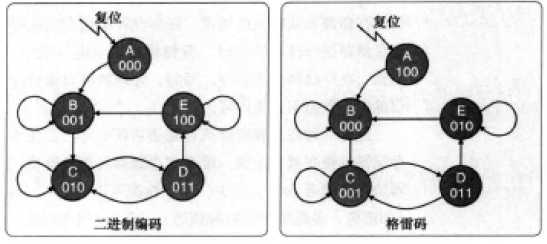

图3.1 低功耗设计中二进制编码与格雷码对比

除此之外,对大型状态机进行分解,形成功能相同的两个子FSM,之间 并没有相互转换关系,这样由于在一个FSM激活时可以关闭另一个FSM,从而降低功耗。状态机详细设计 :状态机设计.docx

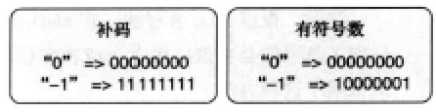

图3.2 补码与有符号数

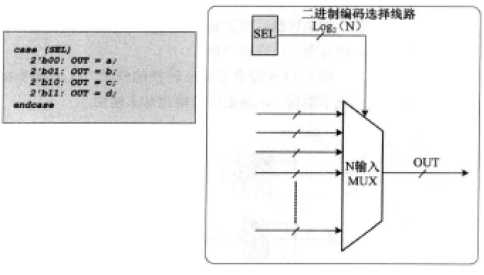

图3.3 MUX选择线路的二进制编码

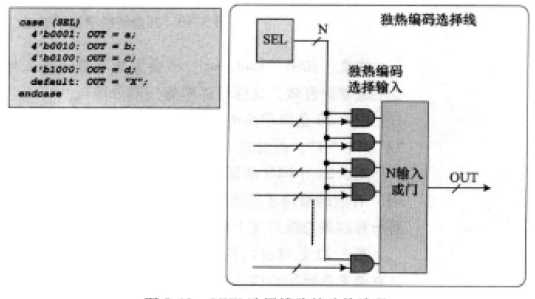

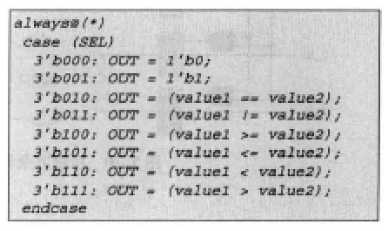

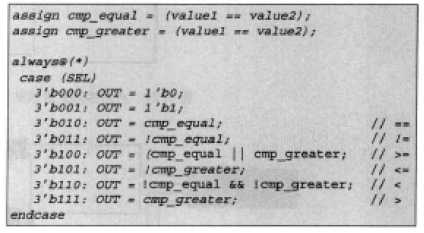

注意,如果MUX的每个输入是多位总线,就会产生明显 的开关过程 ,由此产生功耗 。如果对“case”条件进行编码时按照图3.4所示中的独热码方式,输出会更快更稳定,而且在初期就能将未选中的总线掩藏起来,因此实现 低功耗效果。

图3.4 独热编码case语句

图3.5 冗余转换消耗了能量

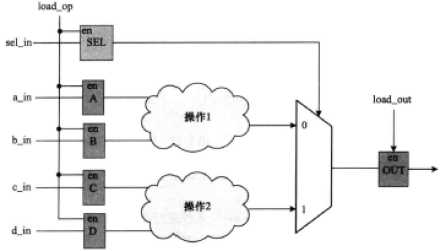

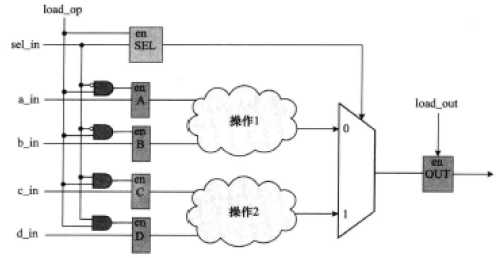

如图所示,如果load_out无效,则load_op也应该无效才不会有输入却没有输出,这样才可以节省功耗。除此之外,只有SEL为0时,AB才有效 ,CD无效,这里又会浪费部分功耗。如图3.6所示为压缩后的电路图。

图3.6 使能ABCD,使其可以有效时输出

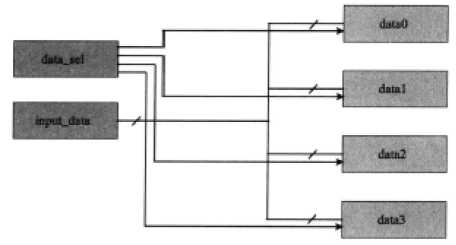

除此之外,在点对多点式的数据总线切换过程中,也会发生冗余转换的现象,如图3.7所示

图3.7 点对多式总线转换

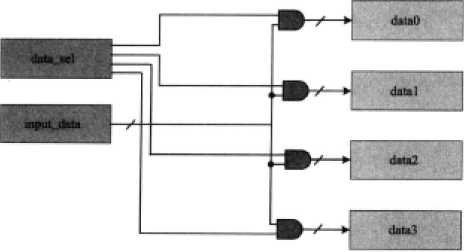

由于data_sel如果并不是全部有效的话,会导致部分数据data输入消耗功耗,却无用。如图3.8为更改后的电路。

图3.8 点对多式数据总线转换

图3.9 未进行资源共享

使用重复的逻辑会增大面积,而且增加功耗。如图3.10所示,通过 先 将其运算出来在进行复用可以 同样实现上述功能且使用资源和面积更小。

图3.10 逻辑复用后的代码

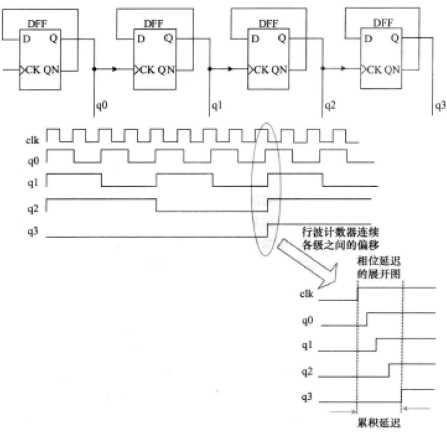

如图3.11所示,为行波计数器的电路结构和导致时钟偏移的时序图。

图3.11 四级行波计数器中的相位延迟

由于越高级的输出相位偏移累加越多,在时钟进行过程中计数器可能会产生不正确的值,产生坏的影响。例如下图3.12所示计数过程,数据由于 延迟 会从0111先变化为0110,0100,0000,最后才回变化为1000,而不是干净的直接变化为1000。

图3.12 计数器由于延迟变化

在许多的使用环境中,这种效应是在课接受 范围内的,是因为行波是快速发生的。比如驱动发光二极管,但是在用于驱动多路选择器或者索引指针时,就会有很大的问题。

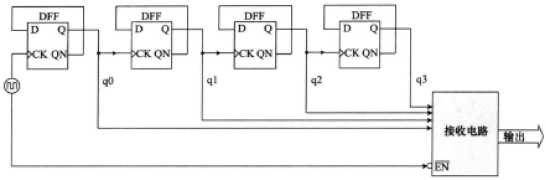

通过对输出数据进行时钟低有效输出,可以 避免行波计数器中毛刺的产生,如图3.13所示。

图3.13 避免毛刺产生的行波计数器

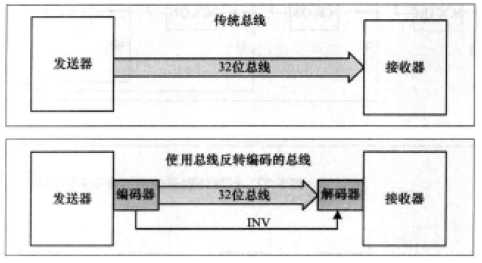

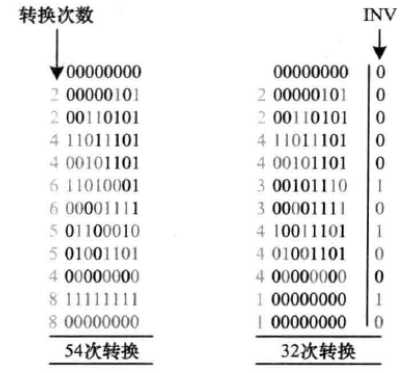

图3.14 总线反转编码

如图3.15是反转后与未反转的数据转换对比图,可以看出反转后的数据转换次数减少不少。

图3.15 反转前后数据转换次数对比

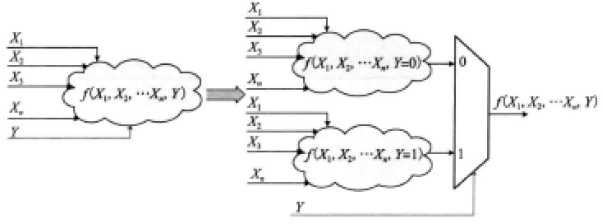

图3.16 逻辑云活跃度划分

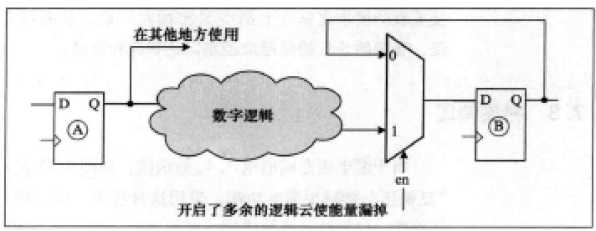

图3.17 使能逻辑云

原文:https://www.cnblogs.com/xianyufpga/p/13644505.html