module divide_3 (

input clk,

input rst_n,

output clk_out

);

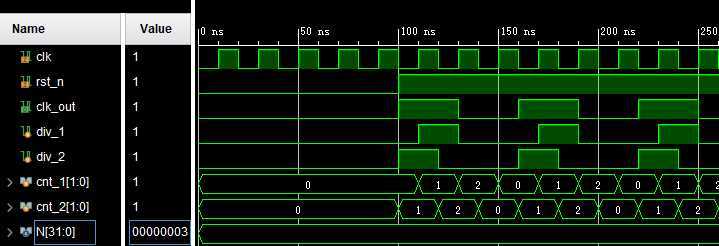

parameter N = 3 ;//分频系数

reg div_1,div_2;

reg [1:0] cnt_1,cnt_2;

assign clk_out = div_1 | div_2 ;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

div_1 <= 0;

cnt_1 <= 0;

end

else if (cnt_1 == N-1) begin

cnt_1 <= 0;

end

else begin

if(cnt_1 == 0)

div_1 <= ~div_1;

else if(cnt_1 == (N-1)/2) begin

div_1 <= ~div_1;

end

cnt_1 <= cnt_1 + 1;

end

end

always@(negedge clk or negedge rst_n) begin

if(!rst_n) begin

div_2 <= 0;

cnt_2 <= 0;

end

else if (cnt_2 == N-1) begin

cnt_2 <= 0;

end

else begin

if(cnt_2 == 0)

div_2 <= ~div_2;

else if(cnt_1 == (N-1)/2 )

div_2 <= ~div_2;

cnt_2 <= cnt_2 + 1;

end

end

endmodule

`timescale 1ns/1ns

module tb_divide_3();

reg clk;

reg rst_n;

wire clk_out;

initial begin

clk = 0;

rst_n = 0;

#100

rst_n = 1;

#1000

$finish;

end

always #10 clk = ~clk;

divide_3 u_divide_3(

.clk(clk),

.rst_n(rst_n),

.clk_out(clk_out)

);

endmodule

原文:https://www.cnblogs.com/pure-z/p/13306190.html