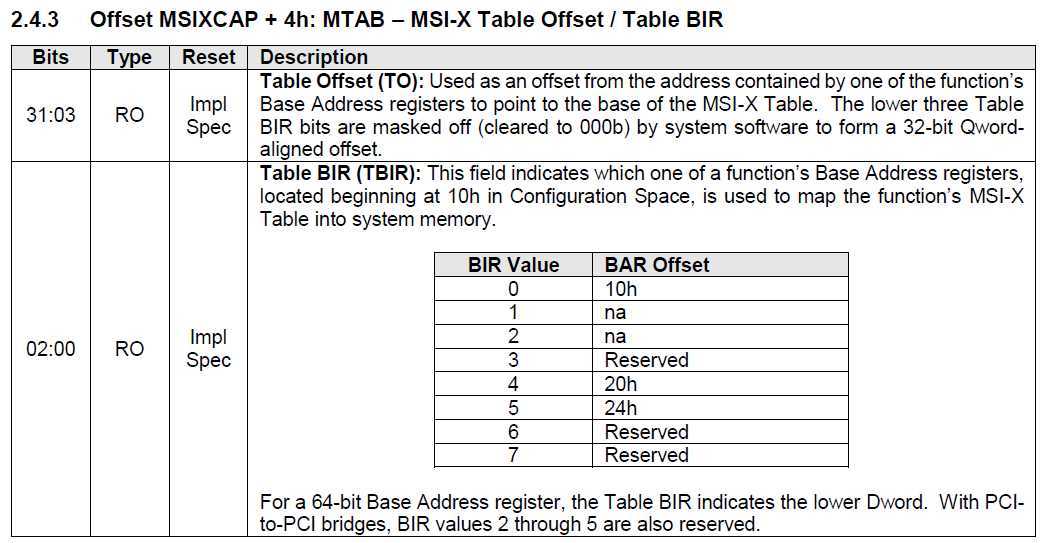

Note: It is recommended that the controller allocate a unique MSI-X vector for each Completion Queue.

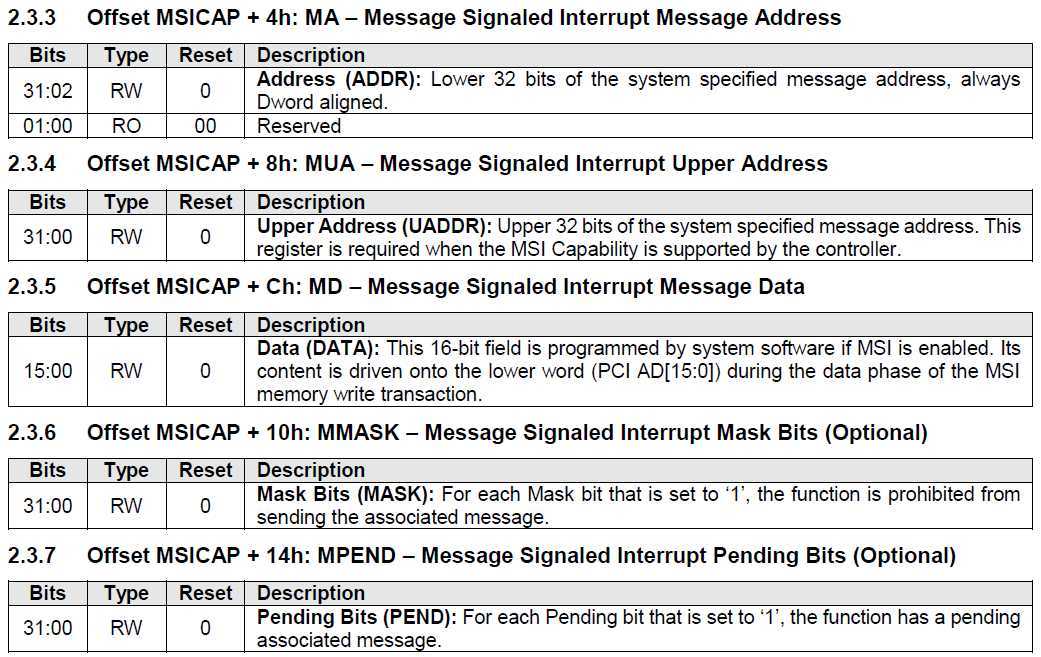

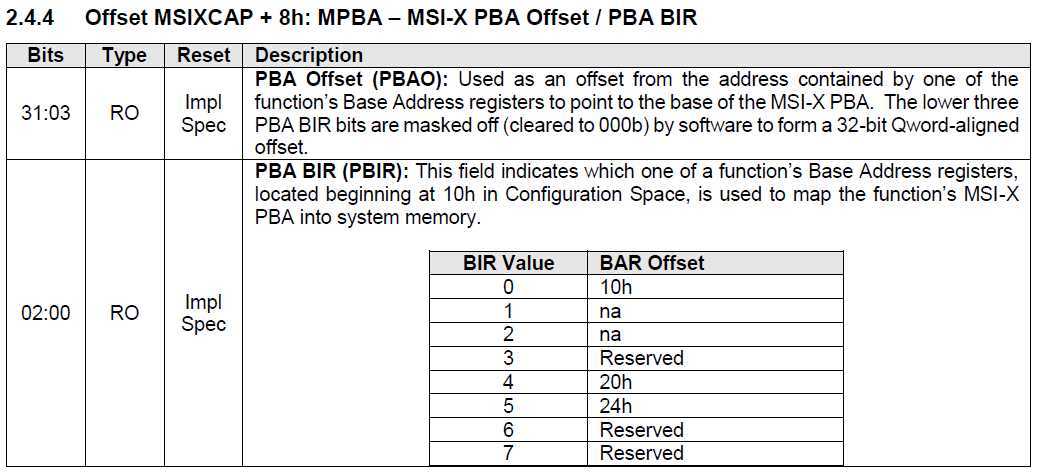

The Table BIR and PBA BIR data structures may be allocated in either BAR0-1 or BAR4-5 in implementations. These tables should be 4KB aligned. The memory page(s) that comprise the Table BIR and PBA BIR shall not include other registers/structures. It is recommended that these structures be allocated in BAR0-1 following the Submission Queue and Completion Queue Doorbell registers. Refer to the PCI reference for more information on allocation requirements for these data structures.

注意:建议控制器为每个完成队列分配一个唯一的MSI-X向量。

在实现中,可以在BAR0-1或BAR4-5中分配表BIR和PBA BIR数据结构。 这些表应对齐4KB。 包含表BIR和PBA BIR的存储器页面不应包括其他寄存器/结构。 建议在提交队列和完成队列门铃寄存器之后的BAR0-1中分配这些结构。 有关这些数据结构的分配要求的更多信息,请参阅PCI参考。

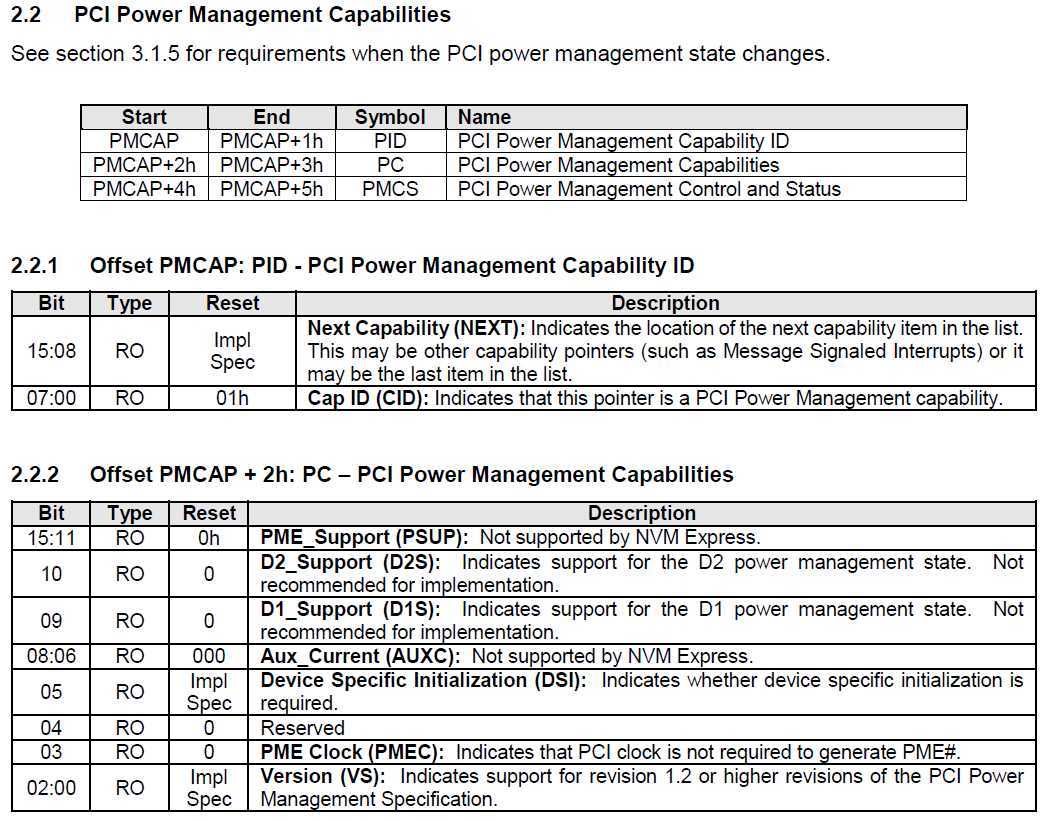

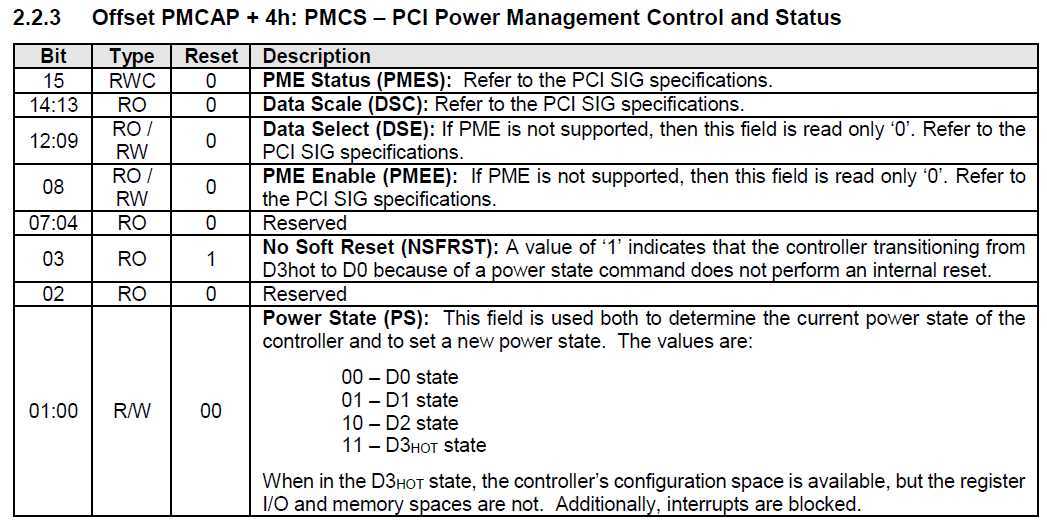

2.2 PCI Power Management Capabilities

原文:https://www.cnblogs.com/hswy/p/12660376.html