我要做CPU_1

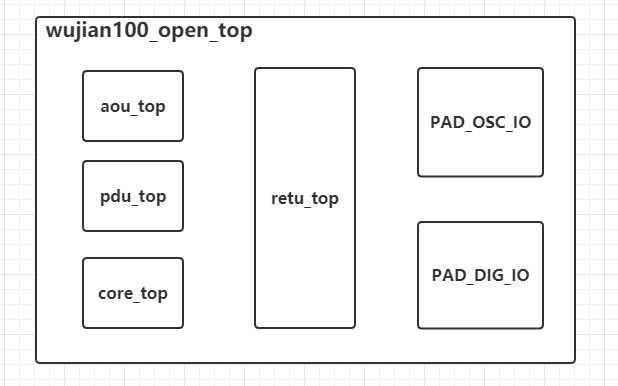

1.wujian100_open_top.v文件分析

首先,我不知道这个工程是干嘛的,能想到的是先理清楚整个工程的架构,然后再分析具体模块实现的功能,已经这些模块之间的外部联系。

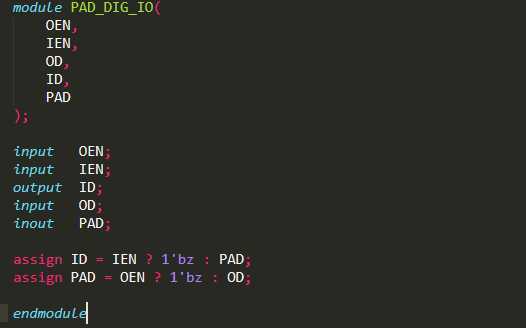

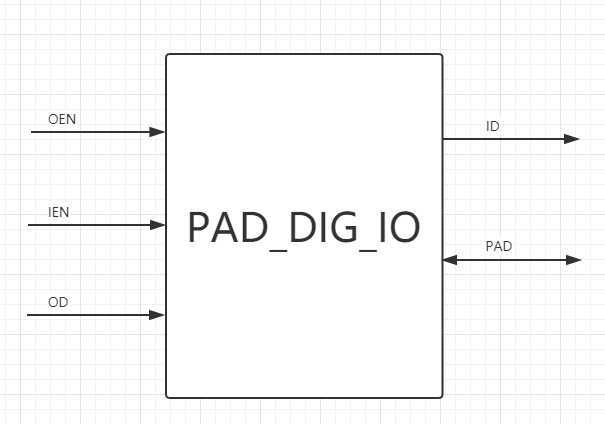

2.PAD_DIG_IO.v文件分析

从比较简单的模块开始,可以看出,这是一个输入输出端口控制模块。

OEN为1时,PAD为输入端口。

OEN为0时,PAD为输出端口。输入端OD的数据直接从PAD传出。

IEN为1时,ID没有输出。

IEN为0时,ID的输出为PAD。

IEN和OEN怎么去配置的,需要进一步阅读代码。

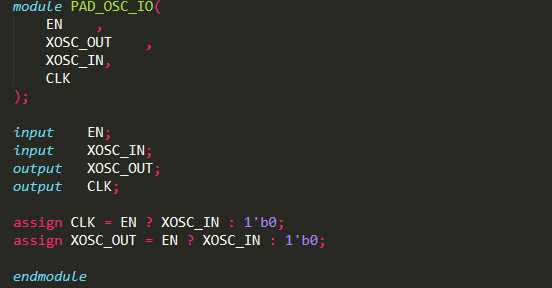

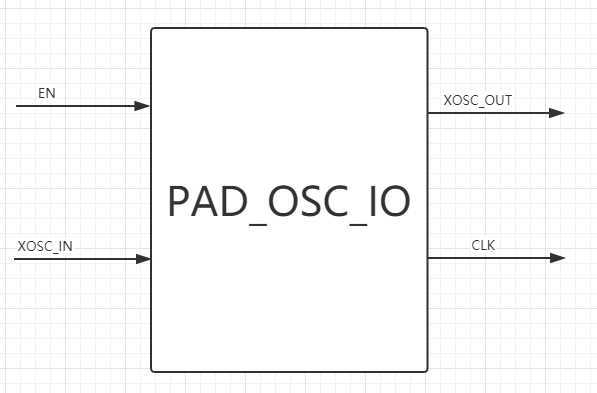

3.PAD_OSC_IO.v文件分析

当EN为1时,输出时钟CLK为XOSC_IN,同样XOSC_OUT也为XOSC_IN,为什么需要这样一个模块呢。

原文:https://www.cnblogs.com/chensimin1990/p/12505818.html