写在前面的话

作为初学者,通常情况下我们所设计的电路都是低速的电路,一般都在百兆以下。那么,当我们需要设计高速电路的时候,就需要用到流水线。本节,梦翼师兄和大家一起初步地学习流水线。

流水线基本概念

流水线的设计,就是指对延时较大的组合逻辑插入寄存器,把较大的组合逻辑拆分成几个时钟周期来完成,以提高系统的最大时钟频率。但是这样做,会导致数据输出的延时,假若插入一个寄存器,则数据输出就到产生一个时钟周期的延时,假若插入N个寄存器,就会产生N个时钟周期的延时,下面我们用两幅图来描述这种关系。

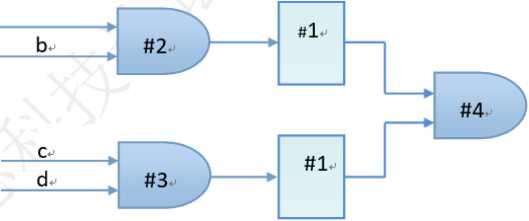

上图的总延时等于max{2,3} + 4 = 7ns;系统的时钟周期必须要大于7ns。当经过流水线改造之后,如下图所示:

经过流水线改造之后,总延时等于max{2,3} + 1 + 4 = 8ns;但是系统的时钟周期只要大于4ns即可(引入了触发器,数据的采集需要发生在时钟上升沿),总处理数据的吞吐量增加了。

流水线改造实例

接下来我们用一个很简单的例子来说明如何对电路进行简单的流水线改造,假设我们现在要实现(4*a+6*b)-10,那么我们可以用原理图的方式来实现这一算法。

首先,跟之前的项目一样,新建一个项目工程。当工程建立完毕之后,我们不需要新建verilog HDL file,而是新建一个Block Diagram / Schematic File,如下图所示:

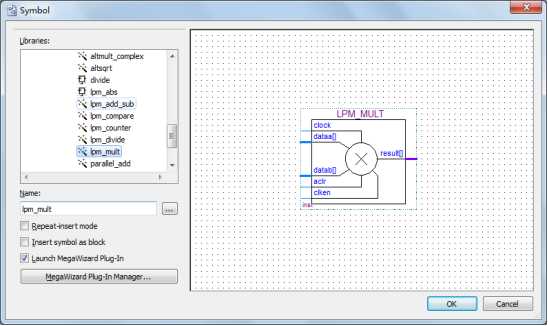

然后我们在新建的原理图里面,双击一下鼠标左键,然后在左上角的library里面找到lpm_mult,如下图所示:

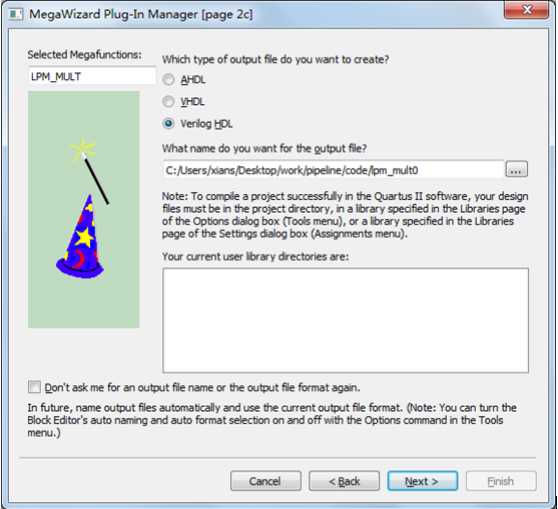

点击【OK】,选择一下程序保存的路径然后选择【NEXT】,如下图所示:

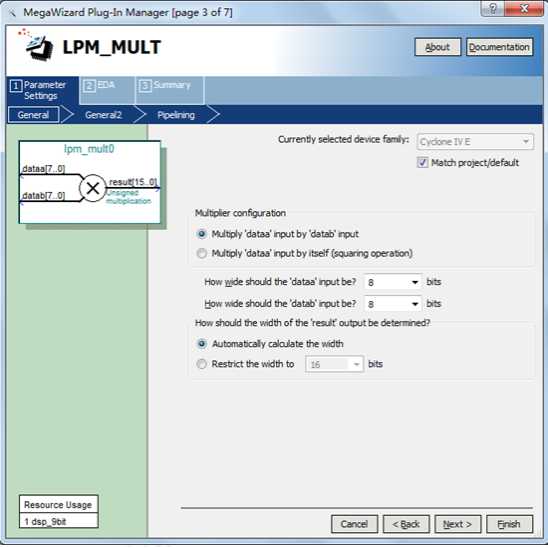

点击【NEXT】之后,会弹出配置乘法器的选项,如下图所示:

这里是选择乘法器的位宽,直接点击【NEXT】得到下图:

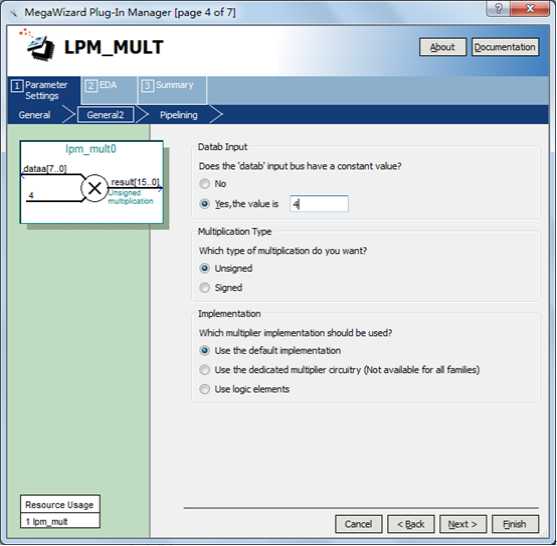

如上图所示,选择让输入的数据乘以一个常数,然后点击【Finish】;同理再新建一个输入的数据乘以常数6的乘法器。

现在我们已经实现了4*a与6*b,接下来我们新建一个加法器双击原理图,在library里面找到lmp_add_sub,然后点击【OK】,选择好程序保存的路径之后,就会出现配置加法的选项,如下图所示:

选择仅仅使用减法,而且把位宽调到16位,然后点击【NEXT】如下图所示:

选择输入的数据减去一个固定的常数,然后选择【Finish】即可。接着我们新建一个Verilog HDL File文件,写一个16位的寄存器组;

代码如下:

|

/**************************************************** * Engineer : 梦翼师兄 * QQ : 761664056 * The module function: 寄存器 *****************************************************/ 00 module reg_data(clk,data_in,data_out); 01 input clk;//时钟输入端口 02 input [15:0]data_in;//数据输入端口 03 04 output reg [15:0]data_out;//数据输入端口 05 06 always@(posedge clk) 07 begin 08 data_out<=data_in;//输出数据等于输入数据 09 end 10 endmodule |

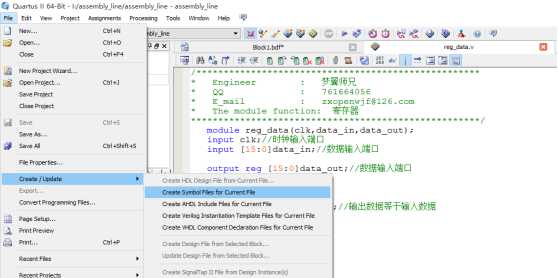

接着我们选择左上角的File,然后选择Creat/Updata,再选择Crear Symbol File,将代码文件转换成原理图文件

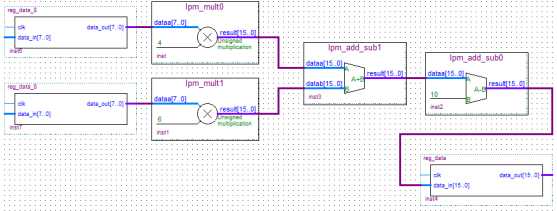

然后我们回到原理图的文件里面,双击原理图,在左上角的library里面会多出一个projet,然后在projet里面找到刚才写的寄存器,然后双击放进原理图里面,然后我们用一样的方法,再新建一个8位位宽的寄存器组,然后放进原理图里面,完成之后把线连接好,如下图所示:

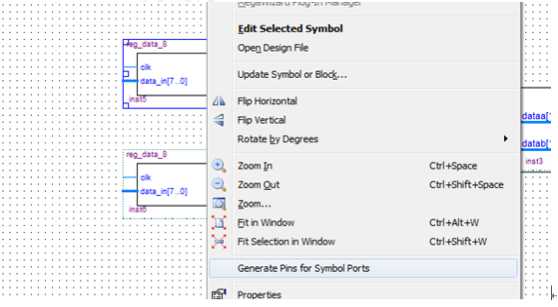

然后还没有接线的模块,可以选择右键,选择Generate Pins for Symbol Ports

然后还没有接线的模块,可以选择右键,选择Generate Pins for Symbol Ports

然后再把未接上的线给全部接上,如下图所示:

然后再把未接上的线给全部接上,如下图所示:

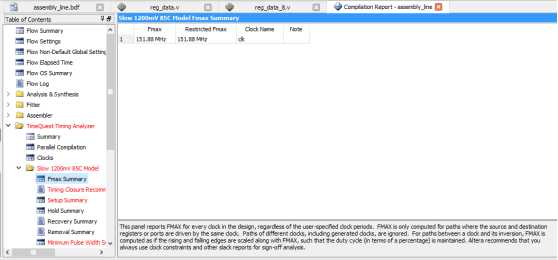

把所以先接上之后,可以按crtl+L,进行全编译,查看静态时序分析,观察系统时钟最大频率是多少。如下图所示:

由上图可知,在还未改造成流水线结构的时候,系统时钟的最大频率是151.88Mhz,然后我们现在开始改造流水线结构(在各节点加入寄存器),看看系统时钟最大频率能上升多少,改流水线结构,如下图所示:

在改造流水线之后,我们可以再一次全编译(ctrl + L),之后我们再继续查看静态时序分析报告,观察系统时钟频率的最大值,如下图所示:

经过流水线改造之后,系统时钟的最大频率由151.88Mhz提升至了303.12Mhz,大幅系统时钟频率。

原文:https://www.cnblogs.com/mengyi1989/p/11521052.html