https://mp.weixin.qq.com/s/CtT08xZON0YxnheqDM2FAw

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

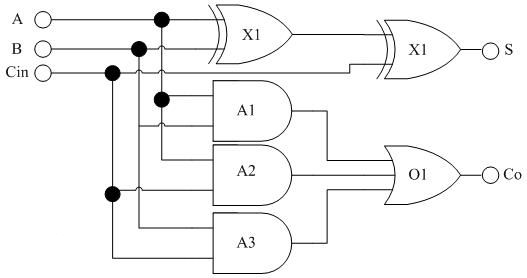

逻辑图

? ?

?

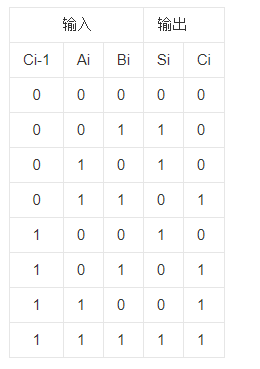

真值表

? ?

?

参考链接

无

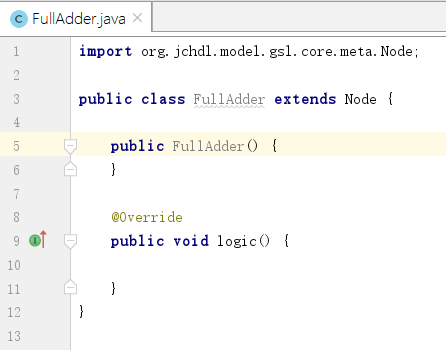

1.创建FullAdder.java, 并生成构造方法和logic()方法

? ?

?

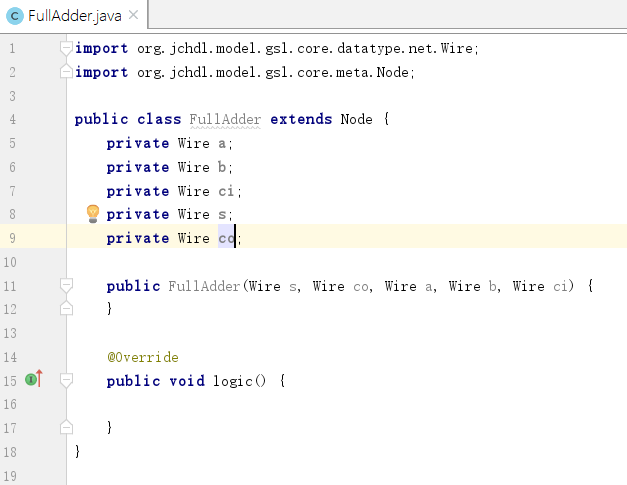

2. 根据逻辑原理图,添加输入输出线

? ?

?

3. 在构造方法中搜集输入输出线并调用construct()方法

? ?

?

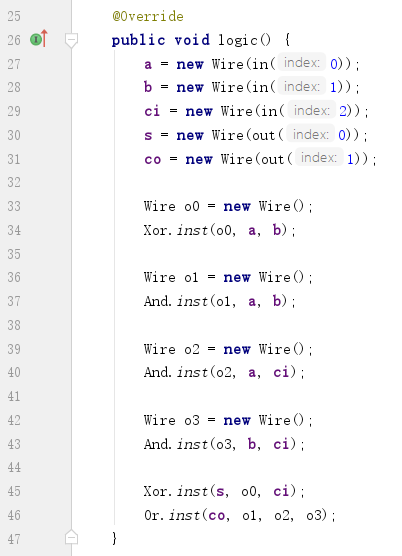

4. 在logic()方法中创建子节点并连线

? ?

?

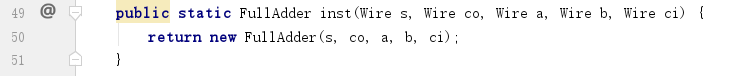

5. 创建inst静态方法方便后续使用

? ?

?

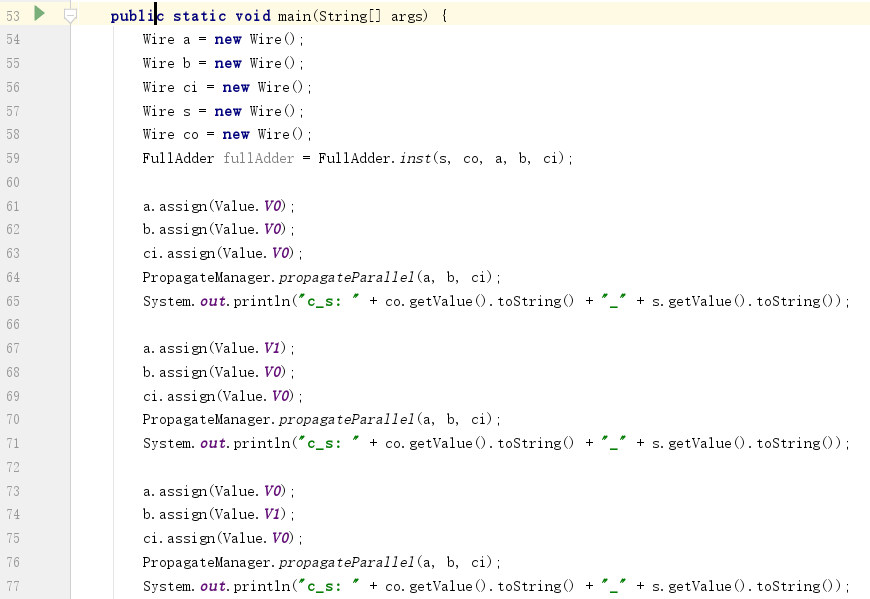

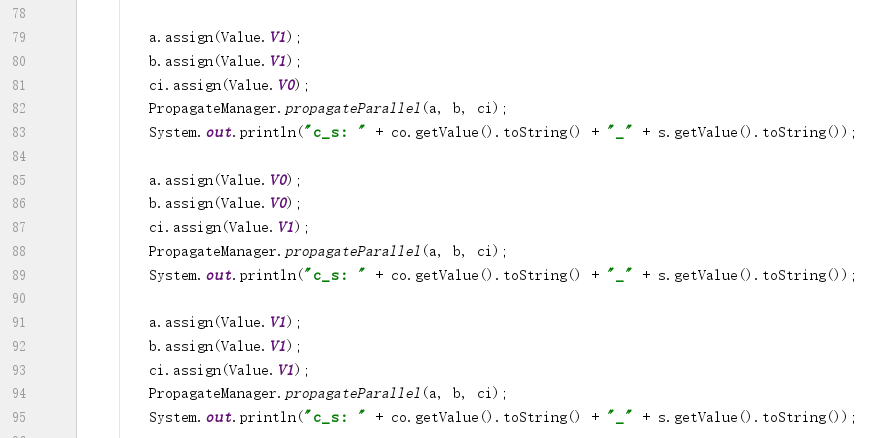

6. 创建main方法执行验证

? ?

?

? ?

?

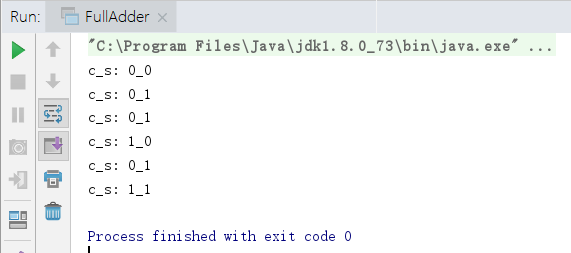

运行结果为:

? ?

?

与真值表一致。

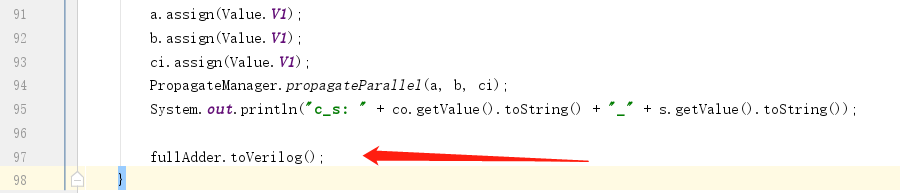

7. 生成Verilog

? ?

?

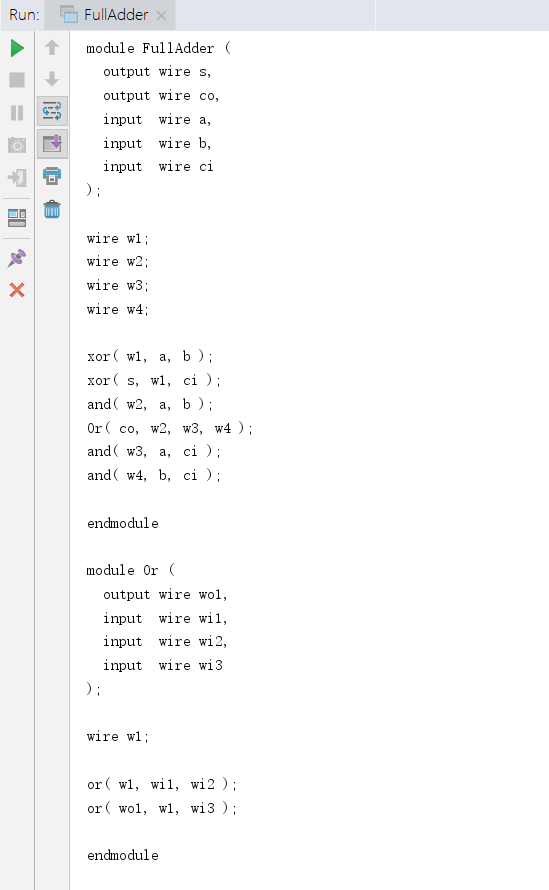

执行结果如下:

? ?

?

jchdl - GSL实例:FullAdder

原文:https://www.cnblogs.com/wjcdx/p/9673961.html