|

文件模块

|

mr_rate_detect

|

|

|

refclock

|

被测时钟

|

|

|

measure_clk

|

参考时钟,为固定100M

|

|

|

reset

|

复位,高电平有效

|

|

|

refclock_measure

|

在一定时间内被测时钟的计数值

|

|

|

valid

|

计数完成时的效指示信号

|

2、cdr_clk时钟的确定

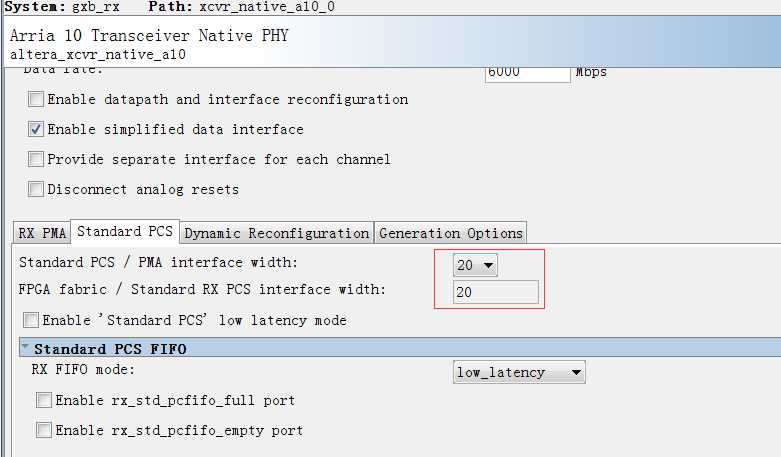

cdr_clk时钟频率做为GXB的参考时钟,该时钟的大小与GXB中数据接收位宽有关,如下图中的设置部分,当接收到的数据线速率为1G时,cdr_clk为1G/8

原文:https://www.cnblogs.com/zhongguo135/p/9438858.html