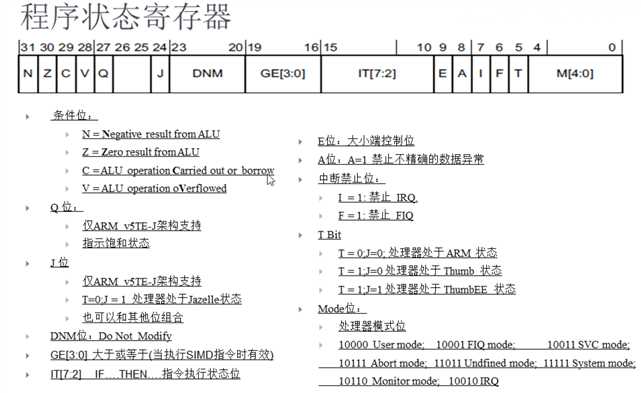

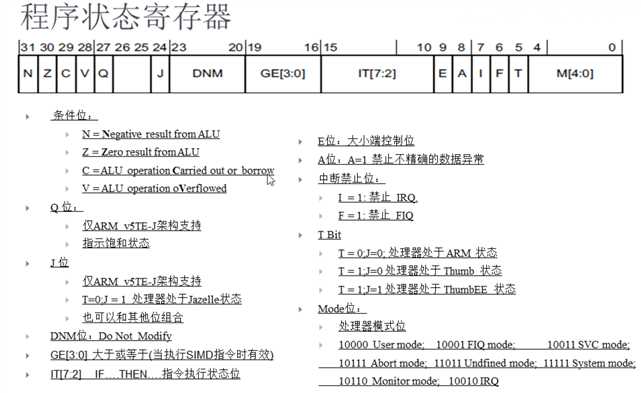

程序状态寄存器(CPSR)

Mode位[4:0]:处理器模式为

USER模式不能直接切换到特权模式,在特权模式下可以直接修改mode位[4:0]为10000,切换到USER模式。

T bit位[5]:处理器状态位

T = 0,J= 0处于ARM指令集状态

T = 1,J= 0处于Thumb指令集状态

T = 1,J = 1处于ThumbEE指令集状态

中断禁止位[7:6]

I = 1 进制IRQ

F = 1 进制FIQ

条件位[31:27]

- N位 Negative result from ALU ALU运算结果为一个负数时, 此为自动置 1 否则为 0

- Z位 Zero result from ALU ALU运算结果为 0 时,此位自动置 1,否则为 0

- C位 分为加法运算和减法运算两种情况:

- 进行加法运算,如果产生进位 C位自动置一

- 进行减法运算时,如果产生借位, C位自动置 0

- V位 符号位溢出,(最高为产生变化,针对于有符号数来说) V位自动置 1

计算机系统中,所有的数据都以 二进制补码 方式存储。

异常处理

ARM 有 7 类中断源:

偏移量 异常类别

- 0x1C FIQ 快速响应中断

- 0x18 IRQ 外部中断

- 0x10 Data Abort 数据终止 当访问数据时,CPU不允许访问请求 会进入此种中断

- 0x0C Perfetch Abort

- 0x08 software interrupt

- 0x04 Undefined Instruction 指令未定义异常 CPU取出一条指令,如果不能执行,此时会 将数据交由协处理器执行。若没有协处理器或者协处理器也不能处理,就会触发此中断

- 0x00 Reset 复位中断

7种异常对应的5种模式

异常源: FIQ IRQ Reset/软中断 DataAbort/PerfetchAbort Undef

CPU模式: FIQ IRQ Supervisor(SVC) Abort Undef

异常处理过程:

当异常产生异常时,ARM core(自动执行但不包括压栈操作):

- 拷贝 CPSR(current program status register)内容到 SPSR_<mode>(saved program status register)<mode>指的是具体哪一个状态的SPSR

- 设置适当的 CPSR 位:

- 改变处理器状态进入ARM状态(处理异常时,必须在ARM状态下进行)

- 改变处理器模式进入相应的异常(特权)模式

- 设置中断禁止位,防止中断处理过程中产生中断(如果需要)

Cortex A系列处理器,不允许同一类的中断嵌套 (处理FIQ时,不响应IRQ;处理IRQ时,可嵌套FIQ)

- 保存返回地址到 lr_<mode>

- 设置 pc 为相应的异常向量

- ARM7、ARM9的异常向量表固定为0x00开始的一端内存中,cortex A系列默认为 0x00 但可以手动设置

返回时,异常处理需要(中断处理程序中手动执行):

- 从 SPSR_<mode>恢复 CPSR

- 从 lr_<mode> 恢复 PC

- Note:这些操作只能在 ARM 状态执行

异常源类型,对应处理器模式。

异常优先级

Reset ——> Data Abort ——> FIQ > IRQ ——> Prefetch Abort ——> SWI→Undefined

FIQ 比 IRQ 快? 三方面原因:

- FIQ优先级高

- FIQ在中断向量表的最高偏移地址,在编程时可以直接在FIQ后面添加中断处理程序,省去了跳转指令。

- FIQ有多个私有寄存器(r8_r14),在中断处理程序中使用这几个寄存器时可以省去压栈,弹栈操作

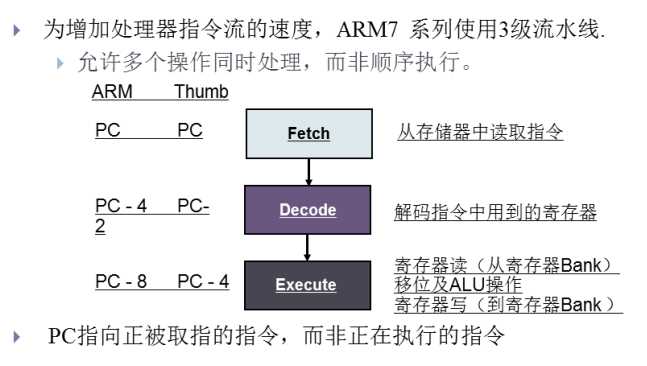

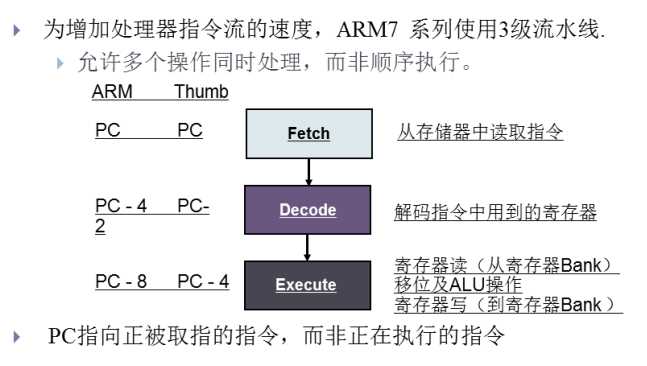

指令流水线

三级流水线:

PC(program count)指向正在取指的指令。

PC - 4 为正在译码的指令。

PC - 8 为正在执行的指令。

ARM体系结构_DAY2

原文:http://www.cnblogs.com/chen-farsight/p/6065487.html