虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的。

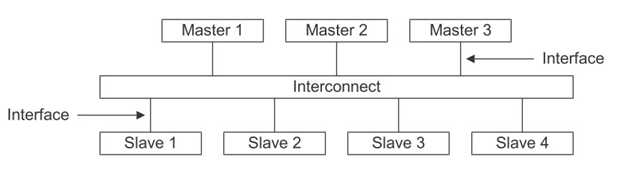

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

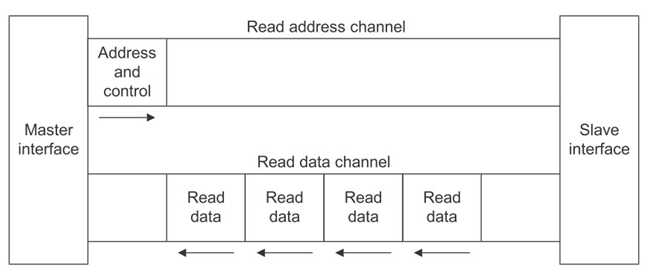

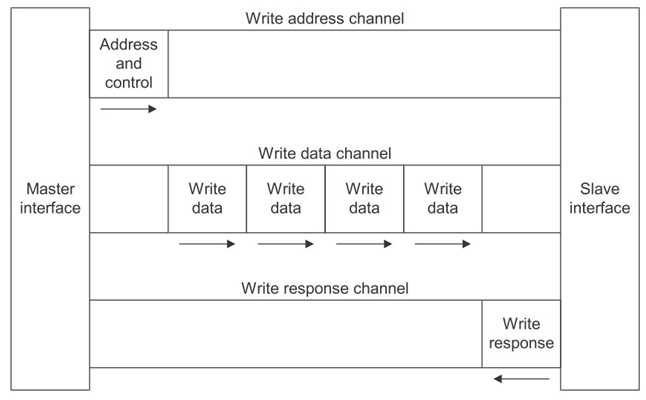

AXI总线是一种基于burst的传输总线,分为5个通道:read address, read data, write address, write data, write response。

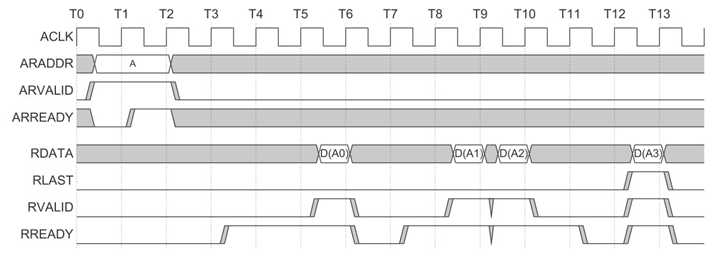

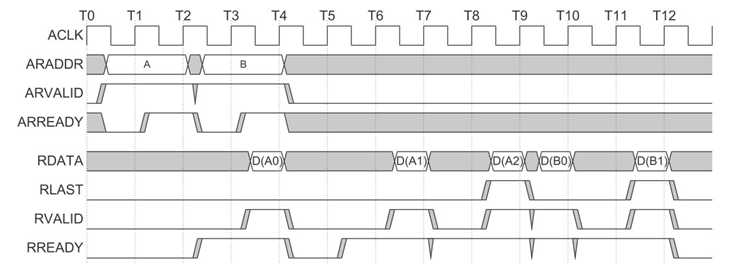

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持VALID为低直到读数据有效。为了表明一次突发式读写的完成,设备用RLAST信号来表示最后一个被传输的数据。

设备会在第一次突发式读完成后处理第二次突发式读数据。也就意味着,主机一开始传送了两个地址给设备。设备在完全处理完第一个地址的数据之后才开始处理第二个地址的数据。

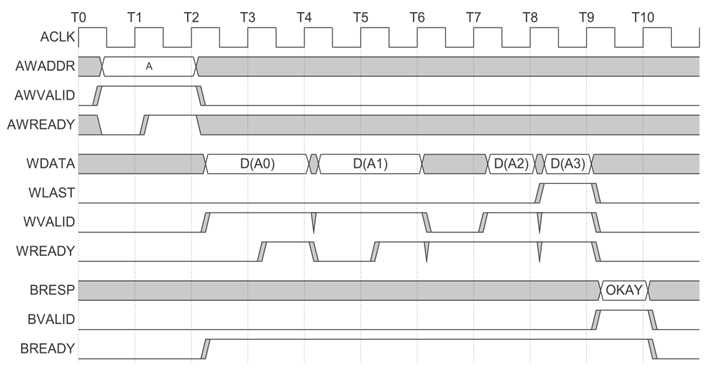

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

信号说明:

1、全局信号

|

信号 |

源 |

描述 |

|

ACLK |

Clock source |

全局时钟信号 |

|

ARESETn |

Reset source |

全局复位信号,低电平有效 |

2、写地址通道信号

|

信号 |

源 |

描述 |

|

AWID[3:0] |

主机 |

写地址ID,这个信号是写地址信号组的ID tag。 |

|

AWADDR[31:0] |

主机 |

写地址。 |

|

AWLEN[3:0] |

主机 |

突发式写的长度。此长度决定突发式写所传输的数据的个数。 |

|

AWSIZE[2:0] |

主机 |

突发式写的大小。 |

|

AWBURST[1:0] |

主机 |

突发式写的类型。 |

|

AWLOCK[1:0] |

主机 |

锁类型。 |

|

AWCACHE[3:0] |

主机 |

Cache类型。这信号指明事务的bufferable、cacheable、write-through、write-back、allocate attributes信息。 |

|

AWPROT[2:0] |

主机 |

保护类型。 |

|

AWVALID |

主机 |

写地址有效。 1 = 地址和控制信息有效 0 = 地址和控制信息无效 这个信号会一直保持,直到AWREADY变为高。 |

|

AWREADY |

设备 |

写地址准备好。这个信号用来指明设备已经准备好接受地址和控制信息了。 1 = 设备准备好 0 = 设备没准备好 |

3、写数据通道信号

|

信号 |

源 |

描述 |

|

WID[3:0] |

主机 |

写ID tag,WID的值必须与AWID的值匹配 |

|

WDATA[31:0] |

主机 |

写的数据。 |

|

WSTRB[3:0] |

主机 |

写阀门。WSTRB[n]标示的区间为WDATA[(8*n)+7:(8*n)]

|

|

WLAST |

主机 |

写的最后一个数据。 |

|

WVALID |

主机 |

写有效 1 = 写数据和阀门有效 0 = 写数据和阀门无效 |

|

WREADY |

设备 |

写就绪。指明设备已经准备好接受数据了 1 = 设备就绪 0 = 设备未就绪 |

4、写响应通道信号

|

信号 |

源 |

描述 |

|

BID[3:0] |

设备 |

响应ID , 这个数值必须与AWID的数值匹配。 |

|

BRESP[1:0] |

设备 |

写响应。这个信号指明写事务的状态。可能有的响应:OKAY、EXOKAY、SLVERR、DECERR。 |

|

BVALID |

设备 |

写响应有效。 1 = 写响应有效 0 = 写响应无效 |

|

BREADY |

主机 |

接受响应就绪。该信号表示主机已经能够接受响应信息。 1 = 主机就绪 0 = 主机未就绪 |

5、读地址通道信号

|

信号 |

源 |

描述 |

|

ARID[3:0] |

主机 |

读地址ID。 |

|

ARADDR[31:0] |

主机 |

读地址。 |

|

ARLEN[3:0] |

主机 |

突发式读长度。 |

|

ARSIZE[2:0] |

主机 |

突发式读大小。 |

|

ARBURST[1:0] |

主机 |

突发式读类型。 |

|

ARLOCK[1:0] |

主机 |

锁类型。 |

|

ARCACHE[3:0] |

主机 |

Cache类型。 |

|

ARPROT[2:0] |

主机 |

保护类型。 |

|

ARVALID |

主机 |

读地址有效。信号一直保持,直到ARREADY为高。 1 = 地址和控制信息有效 0 = 地址和控制信息无效 |

|

ARREADY |

设备 |

读地址就绪。指明设备已经准备好接受数据了。 1 = 设备就绪 0 = 设备未就绪 |

6、读数据通道信号

|

信号 |

源 |

描述 |

|

RID[3:0] |

设备 |

读ID tag。RID的数值必须与ARID的数值匹配。 |

|

RDATA[31:0] |

设备 |

读数据。 |

|

RRESP[1:0] |

设备 |

读响应。这个信号指明读传输的状态:OKAY、EXOKAY、SLVERR、DECERR。 |

|

RLAST |

设备 |

读事务传送的最后一个数据。 |

|

RVALID |

设备 |

读数据有效。 1 = 读数据有效。 0 = 读数据无效。 |

|

RREADY |

主机 |

读数据就绪。 1 = 主机就绪 0 = 主机未就绪 |

7、低功耗接口信号

|

信号 |

源 |

描述 |

|

CSYSREQ |

CLOCK controller |

系统低功耗请求。此信号来自系统时钟控制器,使外围设备进入低功耗状态。 |

|

CSYSACK |

外围设备 |

低功耗请求应答。 |

|

CACTIVE |

外围设备 |

Clock active 1 = 外围设备时钟请求 0 = 外围设备时钟无请求 |

zedboard如何从PL端控制DDR读写(二)——AXI总线

原文:http://www.cnblogs.com/christsong/p/5674733.html