沿检测技术在项目应用中, 非常低广泛。 如要有效捕获信号跳变沿, 边沿 检测技术的应用是必不可少的。大致如下:

(1) 将时钟边沿使能转换为边沿检测使能,使时钟同步化。

(2) 捕获信号的突变( UART, SPI等信号使能突变)。

( 3) 逻辑分析仪中信号的边沿检测。

没有十全十美的东西和代码,以下边缘检测代码也存在缺陷:

(1) 增大CLK信号可以增强边沿检测的效率,但不能滤去跳变的杂波。

(2) 减少CLK可以有效滤去跳变的杂波,但不能及时检测到边沿跳变。

( 3) 增加DFF能更好的滤除杂波,寄存信号,但同时检测延时大。

`timescale 1ns / 100ps

module led_test_top(

input iclk,

input irst,

input trigger,

output pos_trigger,

output neg_trigger

);

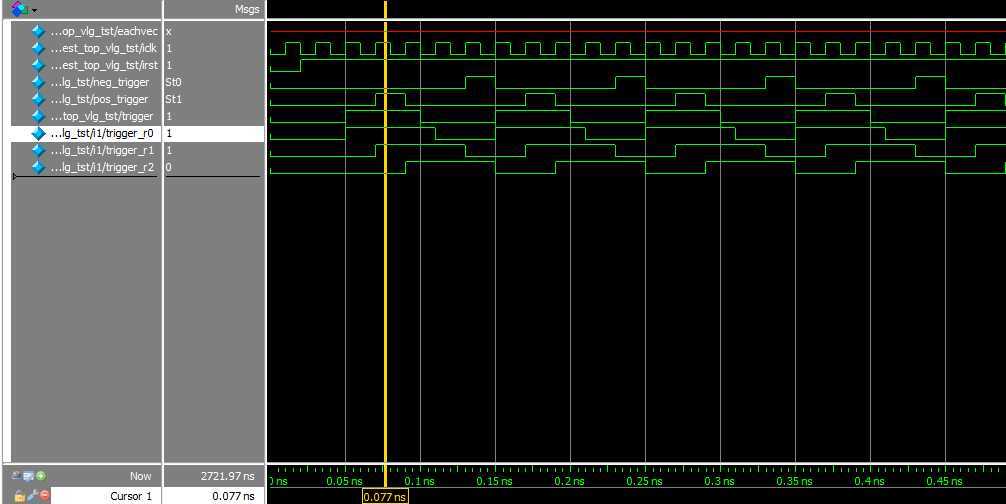

reg trigger_r0;

reg trigger_r1;

reg trigger_r2;

always @(posedge iclk or negedge irst)

begin

if(!irst) begin

trigger_r0 <= 1‘b0;

trigger_r1 <= 1‘b0;

trigger_r2 <= 1‘b0;

end

else begin

trigger_r0 <= trigger;

trigger_r1 <= trigger_r0;

trigger_r2 <= trigger_r1;

end

end

assign pos_trigger = trigger_r1 & ~trigger_r2;

assign neg_trigger = ~trigger_r1 & trigger_r2;

endmodule

原文:http://www.cnblogs.com/mouou/p/5048713.html